Flere muligheder

Design af forbindelser til datacentre

BY: GALAXY

10 months ago

Kunstig intelligens (AI) har fået så meget opmærksomhed de seneste år, at meget få områder af det moderne liv ikke på nogen måde drager fordel af AI eller maskinlæring (ML). Denne vækst har skabt enorme krav til datacentre. Deres arkitektur har ændret sig for at håndtere den stadigt stigende mængde data, og infrastrukturen, der understøtter den, har udviklet sig parallelt for at sikre pålidelig kommunikation i datacentermiljøet.

Som følge heraf må datacentre tage højhastighedsløsninger med lav latenstid i brug for at følge med de udviklende arbejdsbelastninger. En ny tendens kaldet disaggregation har gjort dette behov endnu mere kritisk.

Typiske arkitekturer giver hver processor sin egen hukommelse. Dette holder latenstiden lav, men resulterer i ineffektiv udnyttelse af hukommelsesressourcer. Da kravene varierer over tid, kan en processor opleve en periode med lav aktivitet, mens en anden er overbelastet. Resultatet er en situation, hvor det overbelastede modul har utilstrækkelig hukommelseskapacitet, mens et tilstødende modul har hukommelse til overs.

Disaggregation fjerner hukommelsen fra hver processor og samler den for at skabe en enkelt ressource, der kan bruges mere effektivt. Denne fysiske adskillelse af hukommelse og processor understreger dog behovet for højtydende forbindelse.

PCIe-designovervejelser for datacentre

Når ingeniører vælger forbindelse til de nyeste datacenterarkitekturer, skal de vælge komponenter, der kan understøtte de nuværende og fremtidige behov i AI-revolutionen. Dette er dog ikke den eneste overvejelse, der påvirker valg af stik. Ingeniører skal sikre, at deres stik kan håndtere den nødvendige datagennemstrømning, er holdbare til langtidsbrug og er kompatible med eksisterende systemer til simple opgraderinger. Peripheral Component Interconnect Express (PCIe)®) er en nøgleforbindelse til højhastigheds interne dataoverførsler i datacentre, der driver de nyeste AI-applikationer.

En anden vigtig bekymring for operatørerne er varmehåndtering. Efterhånden som efterspørgslen efter computerkraft stiger, trækker nogle racks op til 100 kW. Denne effektforøgelse skaber en lignende stigning i den varme, der genereres af udstyret. Den indsats, der kræves for at køle et datacenter, kan udgøre op til 40 procent af dets samlede driftsomkostninger.[1]Ifølge retningslinjerne fra American Society of Heating, Refrigerating and Air-Conditioning Engineers (ASHRAE) ligger de anbefalede omgivelsestemperaturer for datacentre mellem 18°C og 27°C (64,4°F til 80,6°F).[2]Efterhånden som energipriserne stiger, opererer mange operatører nu i den øvre ende af dette interval.

Stik spiller en stor rolle i termisk styring. Som nogle af de største komponenter på moderne printplader (PCB'er) kan deres størrelse og placering påvirke luftstrømmen og direkte påvirke, hvor effektivt systemet forbliver køligt.

Det er også vigtigt at forstå temperaturens effekt på stikkets ydeevne. En høj tæthed af aktive komponenter eller ujævn afkøling kan skabe hotspots. Stik skal ikke påvirkes af højere temperaturer, ikke blot af sikkerhedsmæssige årsager, men også for at opretholde stikkets effektivitet. Ved høje temperaturer er det nødvendigt at reducere den elektriske strøm, der passerer gennem en stik, for at forhindre yderligere varme.

Det betyder, at designere skal balancere kompatibilitet med eksisterende infrastruktur, maksimere systemernes kapacitet og behovet for at køle det anvendte system. Stik er afgørende for disse overvejelser.

Næste generations PCIe-stik

For at hjælpe den moderne ingeniør har Amphenol FCI lanceret PCI Express Gen 5 Flip CEM kortkantstik. Den benytter den standard PCIe-grænseflade, hvilket sikrer kompatibilitet med udstyret fra tidligere generationer, der allerede er i drift (Figur 1).[3]Dog giver designfunktionerne for Gen 5-stikket nøglefordele for de nyeste datacenterapplikationer.

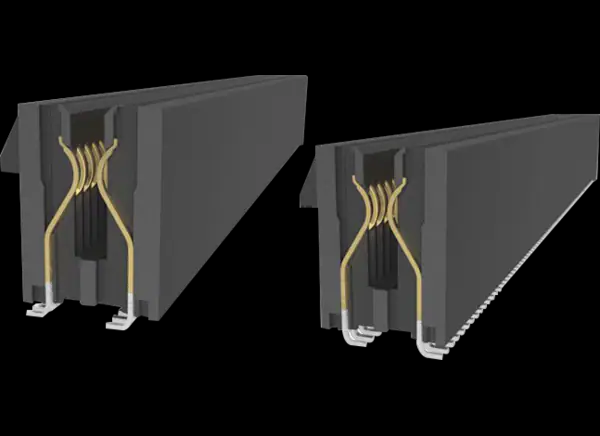

Figur 1:Amphenol FCI PCI Express Gen 5 Flip CEM kortkantstik er kompatible med eksisterende udstyr og sparer op til 19,5 procent plads i PCB-udeladningsområder. (Kilde: Mouser Electronics)

Traditionelle PCIe-stik har to rækker kontakter, hver arrangeret i 180° retning i forhold til hinanden, hvilket skaber et PCB-fodaftryk, der er større end stikkroppen. Til sammenligning justerer Amphenol Flip CEM-designet begge rækker af kontakter i samme retning, hvilket reducerer PCB's fodaftryk med op til 19,5 procent. Resultatet er et stik, der er ideelt til applikationer, der skal placeres tæt på kanten af printkortet.

Amphenol Gen 5 PCIe-stikket er kompatibelt med eksisterende udstyr og tilbyder fulde Gen 5-funktioner op til 32GT/s. Dets robuste design understøtter aktuelle datacenterbehov og tilbyder en klar opgraderingsvej, efterhånden som teknologien fortsætter med at udvikle sig.

Konklusion

AI-revolutionen driver appetitten på mere data. Datacenterarkitekturer udvikler sig for at sikre, at de ikke blot opfylder nutidens krav, men også er robuste og fleksible nok til at imødekomme fremtidige krav.

Amphenol har mange års erfaring med at forfine PCIe-grænsefladen og har udviklet Gen 5 Flip-stikket for at understøtte udviklende datacenterbehov, samtidig med at kompatibiliteten med eksisterende udstyr bevares.

Forfatter

David Pike

Kilder

[1]https://restservice.epri.com/publicdownload/000000003002028905/0/Product

[2]https://www.ashrae.org//File%20Library/Technical%20Resources/Bookstore/ASHRAE_TC0909_Power_

[3]https://www.mouser.com/new/amphenol/amphenol-pcie-cem-card-edge-connectors/

Hjem

Center