ตัวเลือกเพิ่มเติม

การออกแบบตัวเชื่อมต่อสําหรับศูนย์ข้อมูล

BY: GALAXY

11 months ago

ปัญญาประดิษฐ์ (AI) ได้รับความสนใจอย่างมากในช่วงไม่กี่ปีที่ผ่านมา ซึ่งมีเพียงไม่กี่ด้านของชีวิตสมัยใหม่ที่ไม่ได้รับประโยชน์จาก AI หรือแมชชีนเลิร์นนิง (ML) ไม่ทางใดก็ทางหนึ่ง การเติบโตนี้ได้สร้างความต้องการมหาศาลในศูนย์ข้อมูล สถาปัตยกรรมของพวกเขามีการเปลี่ยนแปลงเพื่อรับมือกับปริมาณข้อมูลที่เพิ่มขึ้นเรื่อย ๆ และโครงสร้างพื้นฐานที่รองรับได้พัฒนาควบคู่ไปกับการสื่อสารที่เชื่อถือได้ในสภาพแวดล้อมของศูนย์ข้อมูล

ด้วยเหตุนี้ ศูนย์ข้อมูลจึงต้องนําโซลูชันการเชื่อมต่อความเร็วสูงและเวลาแฝงต่ํามาใช้เพื่อให้ทันกับปริมาณงานที่เปลี่ยนแปลงไป แนวโน้มใหม่ที่เรียกว่าการแยกส่วนทําให้ความต้องการนี้มีความสําคัญมากยิ่งขึ้น

สถาปัตยกรรมทั่วไปมีโปรเซสเซอร์แต่ละตัวมีหน่วยความจําของตัวเอง สิ่งนี้ทําให้เวลาแฝงต่ํา แต่ส่งผลให้การใช้ทรัพยากรหน่วยความจําไม่มีประสิทธิภาพ เนื่องจากข้อกําหนดแตกต่างกันไปตามกาลเวลา โปรเซสเซอร์อาจประสบกับช่วงเวลาที่มีกิจกรรมต่ําในขณะที่โปรเซสเซอร์อื่นโอเวอร์โหลด ผลที่ได้คือสถานการณ์ที่โมดูลที่โอเวอร์โหลดมีความจุหน่วยความจําไม่เพียงพอในขณะที่โมดูลที่อยู่ติดกันมีหน่วยความจําสํารอง

การแยกส่วนจะลบหน่วยความจําออกจากโปรเซสเซอร์แต่ละตัวและรวมเข้าด้วยกันเพื่อสร้างรีซอร์สเดียวที่สามารถใช้งานได้อย่างมีประสิทธิภาพมากขึ้น อย่างไรก็ตาม การแยกหน่วยความจําและโปรเซสเซอร์ทางกายภาพนี้เน้นย้ําถึงความจําเป็นในการเชื่อมต่อประสิทธิภาพสูง

ข้อควรพิจารณาในการออกแบบ PCIe สําหรับศูนย์ข้อมูล

เมื่อเลือกการเชื่อมต่อสําหรับสถาปัตยกรรมศูนย์ข้อมูลล่าสุดวิศวกรต้องเลือกส่วนประกอบที่สามารถรองรับความต้องการในปัจจุบันและอนาคตของการปฏิวัติ AI อย่างไรก็ตาม นี่ไม่ใช่ข้อพิจารณาเพียงอย่างเดียวที่ส่งผลต่อการเลือกตัวเชื่อมต่อ วิศวกรต้องแน่ใจว่าตัวเชื่อมต่อของตนสามารถจัดการกับปริมาณข้อมูลที่ต้องการ ทนทานสําหรับการใช้งานในระยะยาว และเข้ากันได้กับระบบที่มีอยู่เพื่อการอัปเกรดอย่างง่าย การเชื่อมต่อระหว่างส่วนประกอบต่อพ่วง Express (PCIe®) เป็นการเชื่อมต่อระหว่างกันที่สําคัญสําหรับการถ่ายโอนข้อมูลภายในความเร็วสูงในศูนย์ข้อมูลที่ขับเคลื่อนแอปพลิเคชัน AI ล่าสุด

ข้อกังวลที่สําคัญอีกประการหนึ่งสําหรับผู้ปฏิบัติงานคือการจัดการความร้อน เมื่อความต้องการพลังการประมวลผลเพิ่มขึ้น ชั้นวางบางตัวจึงดึงได้มากถึง 100kW การเพิ่มพลังงานนี้ทําให้เกิดความร้อนที่เกิดจากอุปกรณ์เพิ่มขึ้นในลักษณะเดียวกัน ความพยายามที่จําเป็นในการทําให้ศูนย์ข้อมูลเย็นลงสามารถคิดเป็น 40 เปอร์เซ็นต์ของต้นทุนการดําเนินงานทั้งหมด[1]ตามแนวทางของ American Society of Heating, Refrigerating and Air-Conditioning Engineers (ASHRAE) อุณหภูมิแวดล้อมที่แนะนําสําหรับศูนย์ข้อมูลอยู่ในช่วง 64.4°F ถึง 80.6°F (18°C ถึง 27°C)[2]เมื่อต้นทุนด้านพลังงานสูงขึ้นผู้ประกอบการหลายรายจึงดําเนินการในระดับที่สูงขึ้นของช่วงนั้น

ตัวเชื่อมต่อมีบทบาทสําคัญในการจัดการความร้อน เนื่องจากส่วนประกอบที่ใหญ่ที่สุดบางชิ้นบนแผงวงจรพิมพ์ (PCB) ที่ทันสมัย ขนาดและตําแหน่งของส่วนประกอบอาจส่งผลต่อการไหลเวียนของอากาศและส่งผลโดยตรงต่อประสิทธิภาพของระบบที่เย็นอยู่เสมอ

สิ่งสําคัญคือต้องเข้าใจผลกระทบของอุณหภูมิต่อประสิทธิภาพของตัวเชื่อมต่อ ส่วนประกอบที่ใช้งานอยู่ความหนาแน่นสูงหรือการระบายความร้อนที่ไม่สม่ําเสมอสามารถสร้างฮอตสปอตได้ ตัวเชื่อมต่อต้องไม่ได้รับผลกระทบจากอุณหภูมิที่สูงขึ้น ไม่ใช่แค่เพื่อความปลอดภัย แต่เพื่อรักษาประสิทธิภาพของตัวเชื่อมต่อเอง ที่อุณหภูมิสูงจําเป็นต้องลดกระแสไฟฟ้าที่ไหลผ่านขั้วต่อเพื่อป้องกันไม่ให้เกิดความร้อนเพิ่มเติม

ซึ่งหมายความว่านักออกแบบจําเป็นต้องสร้างสมดุลระหว่างความเข้ากันได้กับโครงสร้างพื้นฐานที่มีอยู่เพิ่มขีดความสามารถของระบบและความจําเป็นในการทําให้ระบบที่ใช้งานเย็นลง ตัวเชื่อมต่อมีความสําคัญต่อการพิจารณาเหล่านี้

ตัวเชื่อมต่อ PCIe รุ่นต่อไป

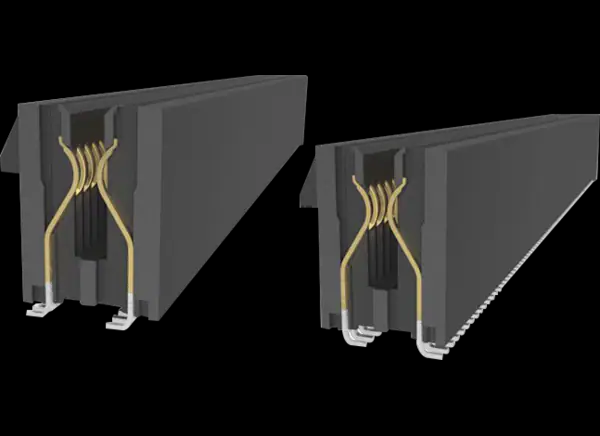

เพื่อช่วยวิศวกรสมัยใหม่ Amphenol FCI ได้เปิดตัวขั้วต่อขอบการ์ด PCI Express Gen 5 Flip CEM ใช้อินเทอร์เฟซ PCIe มาตรฐาน ทําให้มั่นใจได้ถึงความเข้ากันได้กับอาร์เรย์ของอุปกรณ์จากรุ่นก่อนหน้าที่ให้บริการอยู่แล้ว (รูป 1).[3]อย่างไรก็ตาม คุณสมบัติการออกแบบของตัวเชื่อมต่อ Gen 5 มอบข้อได้เปรียบที่สําคัญสําหรับแอปพลิเคชันศูนย์ข้อมูลล่าสุด

รูปที่ 1:ตัวเชื่อมต่อขอบการ์ด Amphenol FCI PCI Express Gen 5 Flip CEM เข้ากันได้กับอุปกรณ์ที่มีอยู่ และประหยัดพื้นที่ได้ถึง 19.5 เปอร์เซ็นต์ในพื้นที่เก็บ PCB (ที่มา: Mouser Electronics)

ตัวเชื่อมต่อ PCIe แบบดั้งเดิมมีหน้าสัมผัสสองแถว โดยแต่ละแถวจัดเรียงในทิศทาง 180° ซึ่งกันและกัน ทําให้เกิดรอยเท้า PCB ที่ใหญ่กว่าตัวเชื่อมต่อ ในทางตรงกันข้าม การออกแบบ Amphenol Flip CEM จะจัดตําแหน่งหน้าสัมผัสทั้งสองแถวในทิศทางเดียวกัน ซึ่งช่วยลดรอยเท้า PCB ได้ถึง 19.5 เปอร์เซ็นต์ ผลลัพธ์ที่ได้คือตัวเชื่อมต่อที่เหมาะสําหรับการใช้งานที่ต้องวางไว้ใกล้กับขอบของ PCB

ตัวเชื่อมต่อ Amphenol Gen 5 PCIe เข้ากันได้กับอุปกรณ์ที่มีอยู่และให้ความสามารถ Gen 5 เต็มรูปแบบสูงสุด 32GT/s การออกแบบที่แข็งแกร่งรองรับความต้องการของศูนย์ข้อมูลในปัจจุบันและนําเสนอเส้นทางการอัปเกรดที่ชัดเจนเมื่อเทคโนโลยีพัฒนาอย่างต่อเนื่อง

สรุป

การปฏิวัติ AI กําลังขับเคลื่อนความต้องการข้อมูลเพิ่มเติม สถาปัตยกรรมศูนย์ข้อมูลกําลังพัฒนาเพื่อให้แน่ใจว่าไม่เพียงแต่ตอบสนองความต้องการในปัจจุบัน แต่ยังแข็งแกร่งและยืดหยุ่นเพียงพอที่จะรองรับความต้องการในอนาคต

Amphenol มีความเชี่ยวชาญหลายปีในการปรับแต่งอินเทอร์เฟซ PCIe และพัฒนาตัวเชื่อมต่อ Gen 5 Flip เพื่อรองรับความต้องการของศูนย์ข้อมูลที่เปลี่ยนแปลงไปในขณะที่ยังคงความเข้ากันได้กับอุปกรณ์ที่มีอยู่

ผู้เขียน

เดวิด ไพค์

แหล่งที่มา

[1]https://restservice.epri.com/publicdownload/000000003002028905/0/Product

[2]https://www.ashrae.org//File%20Library/Technical%20Resources/Bookstore/ASHRAE_TC0909_Power_

[3]https://www.mouser.com/new/amphenol/amphenol-pcie-cem-card-edge-connectors/

บ้าน

ศูนย์